エレファンテック、SustainaCircuits™ 技術による汎用多層基板の開発に成功

発表の概要

エレファンテックでは、インクジェット印刷技術によって銅の使用量を70~80%を削減する革新的な基板 SustainaCircuits™ の量産化を行ってきました。

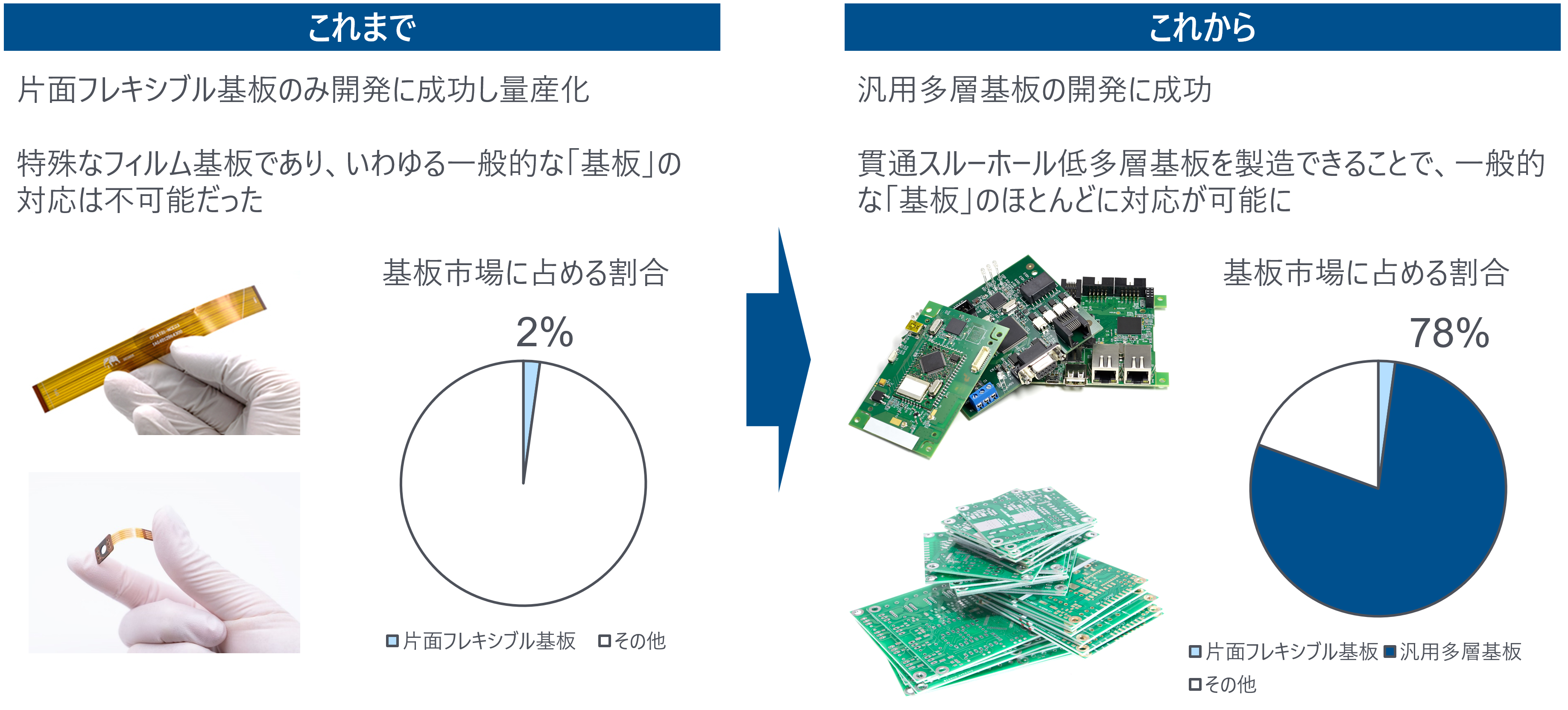

ただし、これまでは片面フレキシブル基板という比較的ニッチな種類の基板しか開発ができていませんでした。片面フレキシブル基板は市場の2%程度に留まり、特に市場の8割1を占める汎用多層基板2への適用が期待されていましたが実現できておらず、2027年以降の実用化を計画していました。

このたび、いくつかの技術革新によって想定より早期に、汎用多層基板の開発に成功しました。主には(1) リジッド基材対応 (2) 多層対応 に成功し、世界の基板の大半の置き換えが可能になりました。

本技術により、CO2排出をはじめとした環境負荷を大幅に削減できるだけでなく、汎用多層基板のコスト構造で大きな割合を占める銅の使用量を70%削減3することを中心に、PCB製造における製造コストを年間1兆円以上削減するポテンシャルが存在すると見込んでいます。

既に複数の電機メーカー様と先行して取り組みを実施しており、2025年前半には試作提供を開始する予定です。

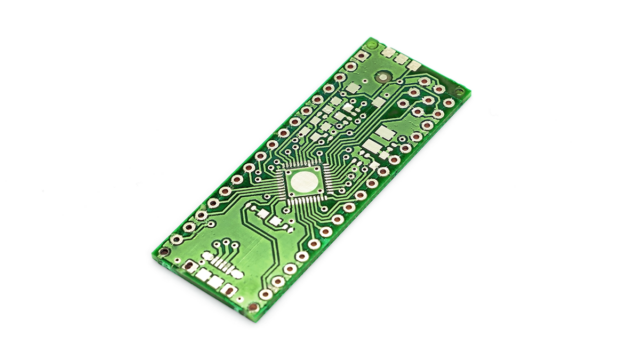

開発した汎用多層基板の写真(4層貫通基板)

開発した汎用多層基板の写真(4層貫通基板)- 面積ベース。半導体サブストレートも含む。数値は2023年富士キメラ総研「FPCの注目アプリケーションと先端技術」及び「エレクトロニクス実装ニューマテリアル便覧」より

- いわゆる低多層RPCBと呼ばれる、1,2,4,6層の汎用リジッド基板を汎用多層基板として定義。層数によらずビルドアップ基板は除いた。

- 配線パターンに依存するが、典型的な値としてこの程度(エレファンテック調べ)

開発に成功した内容

リジッド基材対応

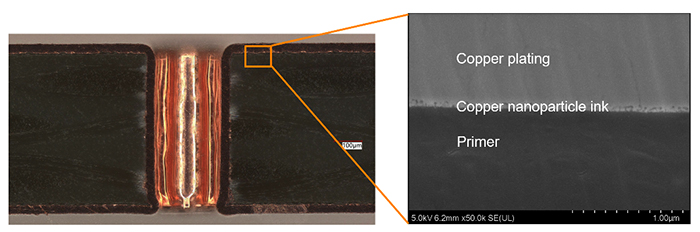

FR-4を含む多くの硬質基材と密着する、プライマーと銅ナノ粒子インクを開発しました。

当社の手がける印刷方式は、平滑な表面に印刷して高い密着性を得る必要があるため、密着性実現という観点では不利であり、これまで十分な密着性が実現できていなかったことがリジッド基材対応の最大の課題でした。

今回、FR-4(ガラスエポキシ基材、汎用多層基板に用いられる)向けに新規開発したプライマーと銅ナノ粒子インクは、FR-4に対して強い密着性を発揮します。特に従来困難であった高温耐性も高く、150℃240hの試験後に1.0N/mm以上※の密着性を実現しており、リジッド基板として活用可能な水準に到達しています。

※UL796規格に準ずる試験方法によるものです。当社測定による参考値であり、保証値ではありません。

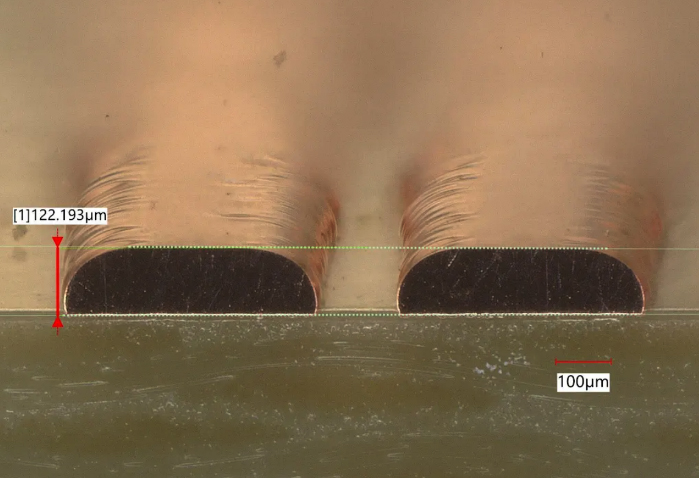

断面構造

断面構造多層化

ビア内にインクを塗布する技術と、プライマーの改良により、多層板・ビアを形成できるようになりました。

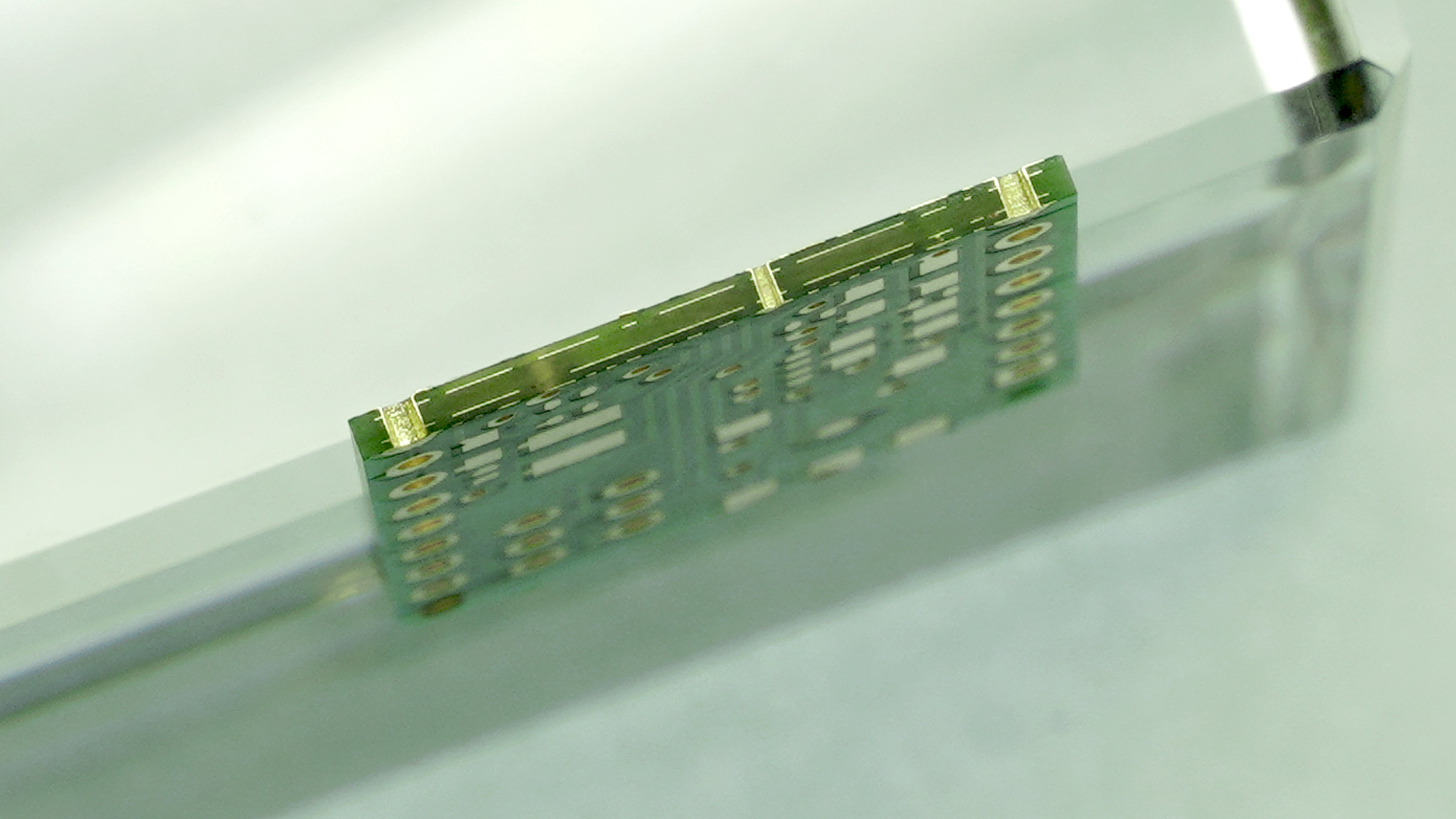

4層基板

4層基板 4層基板の断面

4層基板の断面

8層基板の断面

8層基板の断面

ただし、今回の材料・プロセスは硬質基板向けであり、フィルム基板の多層化には現状では適用できておりません。

微細化

プライマーとインクの組み合わせの改良と、印刷機の精度の改良により、L/S=50/50μmでの配線形成が可能となりました。これまでのL/S=100/100μmから大幅な向上となります。微細化の達成には、プライマー表面でインクが濡れ広がらない必要がありますが、インクが濡れ広がらず弾くようなプライマーでは、描画や密着が難しいという課題がありました。今回開発したプライマーにより、描画性と密着性を担保しつつ、濡れ広がりを最大限抑制することに成功しました。

L/S=50/50μmでの描画比較

L/S=50/50μmでの描画比較大電流対応

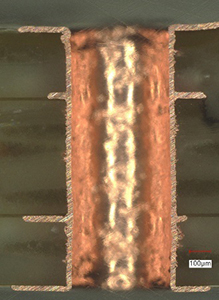

高い密着性・めっき耐性を持つプライマーとインクの開発により、100μm級の銅膜厚の基板も製造可能となりました。

歴史的に、プリンタブル・エレクトロニクスの世界では、流せる電流量に制限があることが普及の大きな課題でした。我々はそのため、印刷プロセスとめっきプロセスを組み合わせたプロセスを提案してきましたが、10μm前後の銅膜厚での対応に留まってきました。信号線には十分ではあるものの、パワーエレクトロニクスには不十分でした。

今回、新規開発したプロセスにより、電気めっきによって100μm級の銅膜厚まで対応が可能になりました。銅価格が着実に上昇する中、必要な部分にだけめっきで銅を形成する工程の経済合理性は、銅の厚みが増えるほど高まります。

100μm超の厚みを持つ配線

100μm超の厚みを持つ配線インパクト

市場の広がり

この技術開発の成功により、世界のPCB市場の78%が置き換え可能になりました。

世界のPCB市場において、これまで面積ベースで2%程度の製品にしか対応できなかったところが、78%に対応可能になります。片面FPCの市場規模は1000万平米程度でしたが、6層以下のリジッド基板は3.7億平米存在します。ほとんどの電子機器に使われている基板は6層以下のリジッド基板であり、特殊な基板を除けばほとんどの基板を置き換え可能となります。

割合は面積ベース、母数に半導体サブストレートを含む。数値は2023年富士キメラ総研「FPCの注目アプリケーションと先端技術」及び「エレクトロニクス実装ニューマテリアル便覧」より

いわゆる低多層RPCBと呼ばれる、1,2,4,6層の汎用リジッド基板を汎用多層基板として定義。層数によらずビルドアップ基板は除いた。

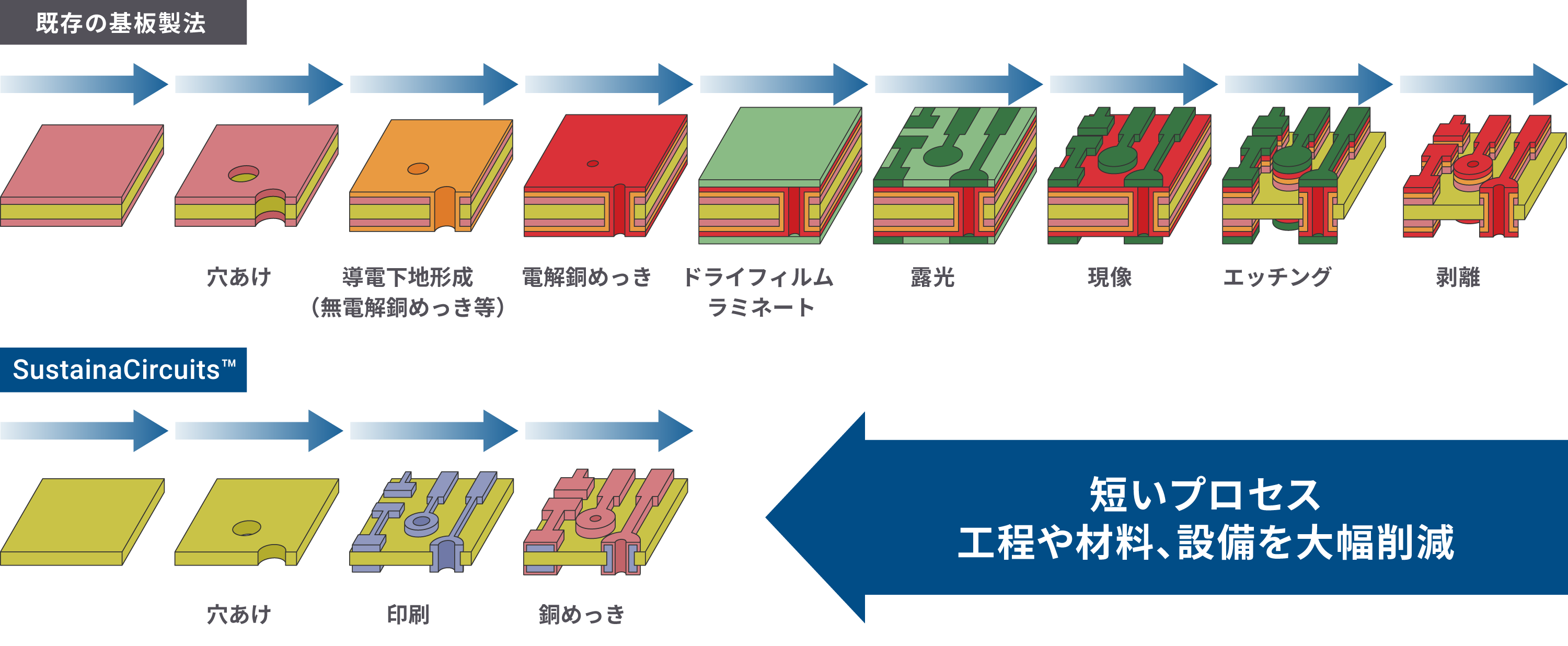

工程削減

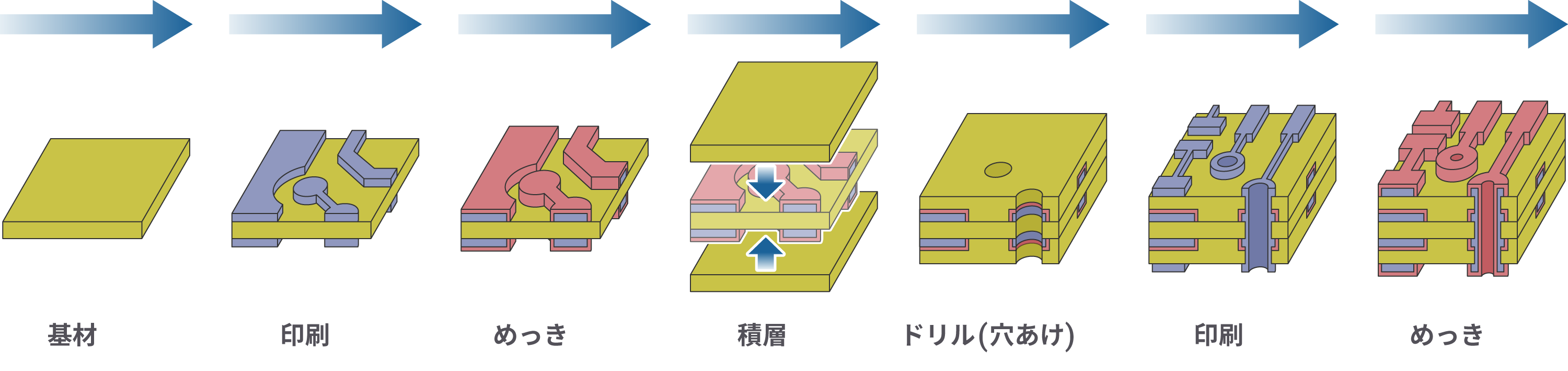

工程削減インパクトは、片面配線よりも多層配線のほうがさらに大きくなります。今回発表した新製法では、ビアと配線を同時に形成することができるためです。

2層基板の製法比較

2層基板の製法比較 4層基板の製法

4層基板の製法銅消費量の削減

本製法によって最も削減インパクトの大きい資源は銅です。多層基板の場合、層数分の銅箔が必要になる上にスルーホールめっきでも銅を消費するため、銅の消費量は大きくなります。

それに対し、本製法では必要な部分にだけ銅を成長させるというプロセスのため、パターン形状にも依存しますが、典型的には70%程度の銅使用量の削減が可能になります。今回開発した汎用多層基板向けで、グローバルに1兆円規模の銅由来コスト削減ポテンシャルがあると試算しております。

- 既存法の内層銅箔35um、外層銅箔18um、めっき厚25umとし、SustainaCircuitsは全層35um、パターン面積比率は30%、平米あたりビア個数は1万穴程度とした

- 2023年富士キメラ総研「エレクトロニクス実装ニューマテリアル便覧」より、2029年の汎用FR-4向け電解銅箔の推定市場規模に、銅めっき用銅の市場規模を足したもの。銅めっきはめっき厚25umを想定

- コストは銅地金ではなく、銅箔としての価格。2024年11月時点の銅建値1448円/kgをベースに銅箔加工賃の平均単価を足して算出

今後の展開

既に開発拠点にてテストサンプルの製作を行っており、主要な評価項目をクリアした段階です。2025年前半には試作提供を開始し、量産体制の構築を行ってまいります。

本製法によるプリント基板は、従来の汎用多層基板製造工場に、当社印刷装置を導入すれば、印刷工程以外は既存の製造設備を用いて量産することが可能です。供給体制については、自社製造にこだわらず、パートナーへの当社装置・材料の提供も含めた形で構築してまいります。

今回開発した技術の想定対応範囲

| PCB種別 | 多層貫通基板 |

| 基材 | FR-4 |

| 最小/ L S | 50/50μm |

| 最小ビア径 | Φ0.15mm |

| Via種別 | PTH, IVH |

| 銅パターン厚み | 10 – 100µm |

| 層数 | 特段の技術的制約無し |

| ワークサイズ | 特段の技術的制約無し |

| 表面処理 | 特段の技術的制約無し |

会社概要

| 会社名 | エレファンテック株式会社 |

| 設立 | 2014年1月 |

| 本社所在地 | 104-0032 東京都中央区八丁堀四丁目3番8号 |

| 代表 | 代表取締役社長 清水 信哉 |

| 事業内容 | プリンテッド・エレクトロニクス製造技術の開発、および電子部品の製造販売 |

| URL | https://elephantech.com |

発表・取材等について 広報担当 pr@elephantech.co.jp